# Performance Analysis of 2D Dual-Gate MoTe<sub>2</sub> FETs With High-k Dielectrics: A Comparative Study Of HfO<sub>2</sub> And La<sub>2</sub>O<sub>3</sub>

Vikram Pratap Singh<sup>1</sup>, Surendra Kumar<sup>2</sup>, Shivam Verma<sup>3</sup>, Amritanshu Pandey<sup>4</sup> <sup>1</sup>Research Scholar, Dept. of Electronics Engg, IIT-BHU, Varanasi, Uttar Pradesh, India. <sup>2</sup>Assistant Professor, School of Electronics Engineering, MIT Vishwaprayag University, Solapur, Maharashtra, India.

<sup>3</sup>Assistant Professor, Dept. of Electronics Engg, IIT-BHU, Varanasi, Uttar Pradesh, India. <sup>4</sup>Associate Professor, Dept. of Electronics Engg, IIT-BHU, Varanasi, Uttar Pradesh, India. **Emails:** vikrampratapsingh.rs.ece23@itbhu.ac.in<sup>1</sup>, surendray1401@gmail.com<sup>2</sup>, shivam.ece@itbhu.ac.in<sup>3</sup>, apandey.ece@itbhu.ac.in<sup>4</sup>

### Abstract

The proposed work uses MoTe2, a type of Transition Metal Dichalcogenide (TMD) channel material, to investigate a monolayer double-gated 2D-FET configuration. The monolayer double-gated 2D-FET structure is advantageous for ultra-large-scale integration and offers more control over subthreshold parameters. Additionally, these designs offer minimal leakage and excellent control over the channel's current. The design of a double-gated 2D-FET using High-K gate dielectric materials, such as lanthanum dioxide and hafnium oxide, as the gate oxide is covered in this study. A comparison of silicon dioxide transistors of the same size, Hafnium oxide and lanthanum oxide as the gate oxide is performed. The comparison primarily focuses on performance metrics such as transconductance, subthreshold slope, and drain current behavior. Using a High-K dielectric material leads to an increase in ON current, which in turn enhances other parameters such as the subthreshold slope, transconductance, and intrinsic gain.

*Keywords:* Monolayer double-gated 2D-FET; Hafnium Oxide; Lanthanum oxide; High-K Dielectric; Subthreshold Slope; Transconductance.

## 1. Introduction

The demand for downscaling in the upcoming ten years, the number of field-effect transistors (FETs) with channel lengths shorter than 7.5 nm will increase significantly for integrated circuits. But because to issues including short-channel effects, higher drainleakage currents, and excessive power consumption, conventional silicon FETs are physically reaching their limits [1]. Finding substitute materials for potential next-generation silicon as channel possibilities has become crucial in order to overcome these problems. The atomic and uniform thickness, superior gate electrostatic control, and lack of dangling bonds of two-dimensional (2D) semiconductors have generated a lot of research attention. Numerous 2D materials, including as silicene, 2D MoS<sub>2</sub>, black phosphorene, 2D InSe, and 2D Bi<sub>2</sub>O<sub>2</sub>Se, have been the subject of extensive

research into FETs. [2][3]. Scaling MOSFETs has increased transistor density but faces challenges at the nanometer level, such as high leakage currents and Drain Induced Barrier Lowering (DIBL), which weakens gate control. High-K dielectrics like HfO<sub>2</sub> and La<sub>2</sub>O<sub>3</sub> mitigate these issues by improving channel-gate capacitance [4][5]. Thin gate oxides also help resolve this issue, but they are limited by gate leakage. Multigate (two- or three-gate) FETs have shown potential as alternatives to traditional MOSFETs [5]. These additional gates are designed to achieve high capacitance between the channel and gate. As a result, multigate FETs are more efficient than MOSFETs in terms of short-channel effects (SCE). Among all multigate FETs, 2D-FETs are considered the one of the best alternatives to MOSFETs due to their simple alter of structure and easier fabrication in

International Research Journal on Advanced Engineering Hub (IRJAEH) e ISSN: 2584-2137 Vol. 03 Issue: 02 February 2025 Page No: 146-151 <u>https://irjaeh.com</u> <u>https://doi.org/10.47392/IRJAEH.2025.0019</u>

process [6]. This paper presents the simulation and analysis of 2D-FET, including the I<sub>D</sub> versus V<sub>GS</sub> characteristics and subthreshold slope (SS). transconductance versus  $(g_m)$ , and ID V<sub>GS</sub> characteristics of monolayer dual-gated 2D-FET are analyzed for two different materials. Additionally, a high-k dielectric material is employed to examine the I<sub>D</sub> versus V<sub>GS</sub> characteristics and leakage currents.

### 1.1. Proposed Structure: Monolayer Double Gate 2D-FET

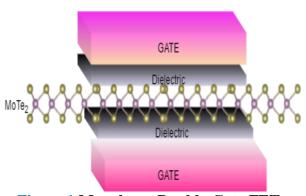

With the growing Researchers and the semiconductor industry have concentrated a lot of work on downsizing Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs) in response to the need for devices that are smaller, more affordable, and have higher performance in accordance with Moore's Law. However, this continuous drive for miniaturization has introduced significant challenges, such as short-channel effects, drain-induced barrier lowering (DIBL), and leakage currents. Extensive research is being conducted to investigate alternative transistor topologies and channel materials for future devices beyond the 10 nm node, as silicon-based approach **MOSFETs** their physical scaling constraints [7][8]. Molybdenum telluride (MoTe<sub>2</sub>) Transistors, which are based on two-dimensional (2D) materials, provide special benefits like reduced leakage currents, efficient gate control, reduced short-channel effects, and high electron mobility (~200  $cm^2/Vs$ ) for high-speed electronics. They are perfect for flexible and wearable devices because of their strength and mechanical flexibility. MoTe<sub>2</sub> transistors also exhibit a high ON/OFF current ratio and thermal stability, making them suitable for harsh environments. These features position MoTe<sub>2</sub> as a key technology for next-generation, scalable, energyefficient, and flexible electronics [9] [10]. Figure 1 below illustrates the two-dimensional field-effect transistor (2DFET) monolayer double-gate (DG). This configuration makes it easier to examine different 2D channel materials and dielectrics and evaluate how they affect the FET's performance, which is crucial for creating transistors with customized threshold voltages. leakage current due to carriers. Understanding the minority charge subthreshold Understanding current helps subthreshold current helps in managing.

**Figure 1** Monolayer Double-Gate FET

The intrinsic TMDs' atomically thin structure and semiconductor characteristics produce a low offstate current (Ioff), which is essential for lowering electronic device power consumption in sleep or idle modes. TMDs are frequently employed as channel materials in field-effect transistors (FETs) by taking advantage of these special properties. Excellent electrostatic channel control, enhanced gate control, and decreased leakage currents are made possible by their atomically thin nature. Moreover, In transistor designs, TMDs work well when integrated with high-k dielectrics. Because of this compatibility, TMD-based transistors are better suited for energyefficient applications since they improve gate control and lower power consumption. [11]. This work enables the exploration of how various When constructing transistors with particular threshold voltages, 2D channel materials and dielectrics have a significant impact on FET performance. MoTe2 was chosen for the device's operation analysis, and TMDs were chosen as the channel material. The transistors' atomic thinness allows them to lessen short-channel effects. is valuable in the pursuit of high-performance electronic devices. Transistor designs with high-k dielectrics can also use TMDs. TMD-based transistors are considerably more attractive for energy-efficient applications because of this compatibility, which enhances gate control and significantly lowers power consumption. When the oxide thickness is reduced beyond 1.2 nm to maintain performance metrics and control shortchannel effects, silicon dioxide begins to lose its dielectric properties. As a result, a new dielectric material is required to prevent electron tunneling [12].

Table 1 presents the dielectric constants of the gate materials utilized in this study, while Table 2 outlines the dimensions of the 2D-FET.

# Table 1 Dielectric Constants of Different Materials

| Material                       | Dielectric Constant |

|--------------------------------|---------------------|

| SiO <sub>2</sub>               | 3.9                 |

| HfO <sub>2</sub>               | 22                  |

| La <sub>2</sub> O <sub>3</sub> | 30                  |

The procedure The 2D electrostatics of the device terms of the carrier continuity equation, 2D Poisson's equation, Shockley-Read-Hall model, and drift-diffusion transport model are solved in order to simulate. [13].

### **Table 2** Dimensions of the 2D-FET

| Parameter           | Value   |  |

|---------------------|---------|--|

| Length along Z-Axis | 0.1 µm  |  |

| Length along Y-Axis | 0.03 µm |  |

| Length along X-Axis | 0.05 µm |  |

| Gate Length         | 20 nm   |  |

As shown in Table 3, a variety of models are employed to examine the device's performance in all dimensions. The different MoTe2 parameters employed in the simulation are shown in Table 4.

Table 3 Physical models used in Simulation

| Model        | Description                                                           |

|--------------|-----------------------------------------------------------------------|

| bqp          | Alternative to density gradient method                                |

| oqp          | and gives better convergence                                          |

| srh          | Used for minority carrier lifetimes                                   |

| ni.fermi     | Fermi statistics effects are included to find intrinsic concentration |

| evsatm<br>od | Defines parallel field mobility model                                 |

| fldmob       | Field dependent mobility is invoked                                   |

# Table 4 Parameters of MoTe2 Used in thisSimulation

| Parameter                  | Value | Unit                                            |

|----------------------------|-------|-------------------------------------------------|

| Thickness                  | 0.8   | nm                                              |

| Lattice constant           | 3.55  | Å                                               |

| Band gap                   | 1.10  | eV                                              |

| Dielectric constant        | 8.46  |                                                 |

| Effective mass of electron | 0.64  |                                                 |

| Effective mass of hole     | 0.78  |                                                 |

| Electron mobility          | 200   | $cm^2V^{-1}s^{-1}$                              |

| Hole mobility              | 20    | $\mathrm{cm}^{2}\mathrm{V}^{-1}\mathrm{s}^{-1}$ |

### 2. Results and Discussion 2.1. Drain Current Characteristics

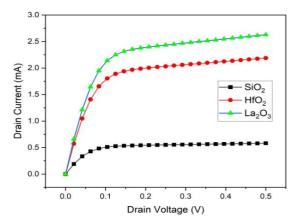

Subthreshold current is defined as the current which flows when the gate voltage is below the threshold voltage. Subthreshold current is essentially the leakage current due to the minority charge carriers. subthreshold current helps Understanding in managing this leakage, which is crucial for maintaining the efficiency and reliability of the integrated circuits (ICs). It affects the performance, power consumption and heat dissipation, requiring the careful design considerations in cutting-edge electronics. ON current is defined as the when the gate voltage is above the threshold voltage ( $V_T$  = 0.3V). The Drain current vs Drain voltage for the MoTe<sub>2</sub> FET with different dielectric materials is shown in Figure 2.

**Figure 2** ID vs VDs for Various Gate Dielectrics In every instance, the gate's dimensions remain constant at 20 nm. The gate voltage vs the drain

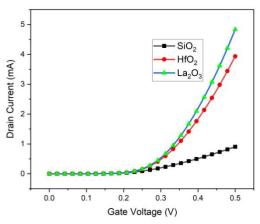

current is shown Figure 3, where we can observe that the ON current for  $La_2O_3$  is highest followed by  $HfO_2$  and  $SiO_2$ .

Figure 3 ID vs VGs for various gate dielectrics.

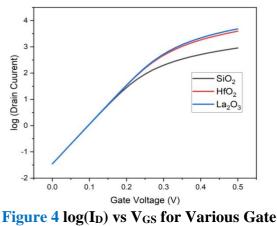

The drain current below the threshold voltage is a non-zero value and increases with the increase in the gate voltage. This subthreshold current can be observed when the  $I_D vs V_{GS}$  graphs are plotted on the logarithmic scale (as shown in the Figure 4).

Dielectrics.

The variation of the subthreshold current can be analyzed by the parameter called Sub-threshold slope.

### 3. Subthreshold Parameters

Under Subthreshold conditions ( $V_{GS}$ <0) the variation of the drain current with respect to the gate voltage is captured using the parameter subthreshold slope [14].

Subthreshold Slope =  $\frac{dV_G}{d(\log_{10} I_D)}$

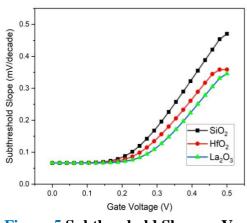

Figure 5 depicts the Subthreshold Slope plotted vs  $V_{GS}$ . As observed from the plot the Subthreshold slope is minimum for La<sub>2</sub>O<sub>3</sub> followed by HfO<sub>2</sub> and then SiO<sub>2</sub>. A lower value of Subthreshold slope indicates small leakage current in the FET under Subthreshold voltages.

**Figure 5 Subthreshold Slope vs V**<sub>GS</sub>

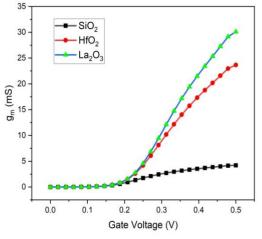

The transconductance  $(\mathbf{g}_m)$  is plotted for various gate voltage values and is shown in Figure 6. The transconductance determines the gain of the amplifier [15].

**Frans conductance** =

$$\frac{dI_D}{dV_{GS}}$$

Figure 6 Trans conductance (gm) vs VGs

Table 5 compares performance metrics for several dielectric materials used in the 2D FET designed using MoTe<sub>2</sub>.

Table 5 Comparison of Performance Parametersfor Different Dielectric Materials used in the 2DEET

| Parameter             | SiO <sub>2</sub> | HfO <sub>2</sub> | La <sub>2</sub> O <sub>3</sub> |

|-----------------------|------------------|------------------|--------------------------------|

| Ion (µA)              | .193             | .48              | .571                           |

| I <sub>off</sub> (µA) | 0.03467          | 0.03597          | 0.03655                        |

| Ion/Ioff              | 5537.93          | 13345.22         | 15630.8                        |

| Subthreshold          | 0.177            | 0.144            | 0.112                          |

| slope (mV/dec)        |                  |                  |                                |

| g <sub>m</sub> (mS)   | 3.484            | 17.555           | 22.107                         |

### Conclusion

This paper explores the design and simulation of a monolayer dual gate 2D-FET incorporating high-k gate dielectric materials using the ATLAS SILVACO TCAD tool. Performance comparisons were made with 2D-FETs using SiO<sub>2</sub>, HfO<sub>2</sub>, and La<sub>2</sub>O<sub>3</sub> as gate dielectrics. La<sub>2</sub>O<sub>3</sub> exhibited the highest Ion/Ioff ratio, followed by HfO<sub>2</sub>, both outperforming SiO<sub>2</sub>. Additionally, the subthreshold slope improved by factors of 1.45 and 1.28 for La<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub>, respectively. Transconductance saw significant enhancement, increasing by 6.35 times for La<sub>2</sub>O<sub>3</sub> and 5.03 times for HfO<sub>2</sub> compared to SiO<sub>2</sub>. These findings highlight high-k dielectric materials as promising candidates for gate dielectrics in dual-gate 2D-FETs. Table 5 shows Comparison of Performance Parameters for Different Dielectric Materials used in the 2D FET

#### References

- [1]. Markov, Stanislav, Yanho Kwok, Jun Li, Weijun Zhou, Yi Zhou, and Guanhua Chen. 2019. "Fundamental Limit to Scaling Si Field-Effect Transistors Due to Source-to-Drain Direct Tunneling." IEEE Transactions on Electron Devices 66(3):1167–73. doi: 10.1109/TED.2019.2894967.

- [2]. Meena, Sanju, Neetika Sharma, and Jyotika Jogi. 2023. "Sub-5 Nm 2D Semiconductor-Based Monolayer Field-Effect Transistor: Status and Prospects." Physica Status Solidi (a) 220(11). doi: 10.1002/pssa.202200526.

- [3]. Lemme, Max C., Deji Akinwande, Cedric Huyghebaert, and Christoph Stampfer. 2022."2D Materials for Future Heterogeneous Electronics." Nature Communications

13(1):1392. doi: 10.1038/s41467-022-29001-4.

- [4]. Palumbo, Felix, Chao Wen, Salvatore Lombardo, Sebastian Pazos, Fernando Aguirre, Moshe Eizenberg, Fei Hui, and Mario Lanza. 2020. "A Review on Dielectric Breakdown in Thin Dielectrics: Silicon Dioxide, High- k, and Layered Dielectrics." Advanced Functional Materials 30(18). doi: 10.1002/adfm.201900657.

- [5]. Kanungo, Sayan, Gufran Ahmad, Parikshit Sahatiya, Arnab Mukhopadhyay, and Sanatan Chattopadhyay. 2022. "2D Materials-Based Nanoscale Tunneling Field Effect Transistors: Current Developments and Future Prospects." Npj 2D Materials and Applications 6(1):83. doi: 10.1038/s41699-022-00352-2.

- [6]. Glavin, Nicholas R., Rahul Rao, Vikas Varshney, Elisabeth Bianco, Amey Apte, Ajit Roy, Emilie Ringe, and Pulickel M. Ajayan. 2020. "Emerging Applications of Elemental 2D Materials." Advanced Materials 32(7). doi: 10.1002/adma.201904302.

- [7]. Cavin, R. K., P. Lugli, and V. V. Zhirnov. 2012. "Science and Engineering Beyond Moore's Law." Proceedings of the IEEE 100(Special Centennial Issue):1720–49. doi: 10.1109/JPROC.2012.2190155.

- [8]. Schwierz, Frank, and Juin J. Liou. 2020. "Status and Future Prospects of CMOS Scaling and Moore's Law - A Personal Perspective." Pp. 1–4 in 2020 IEEE Latin America Electron Devices Conference (LAEDC). IEEE.

- [9]. Pradhan, Nihar R., Daniel Rhodes, Simin Feng, Yan Xin, Shahriar Memaran, Byoung-Hee Moon, Humberto Terrones, Mauricio Terrones, and Luis Balicas. 2014b. "Field-Effect Transistors Based on Few-Layered α-MoTe 2." ACS Nano 8(6):5911–20. doi: 10.1021/nn501013c.

- [10]. Larentis, Stefano, Babak Fallahazad, Hema C.P. Movva, Kyounghwan Kim, Amritesh Rai, Takashi Taniguchi, Kenji Watanabe, Sanjay

K. Banerjee, and Emanuel Tutuc. 2017. "Reconfigurable Complementary Monolayer MoTe<sub>2</sub> Field-Effect Transistors for Integrated Circuits." ACS Nano 11(5):4832–39. doi: 10.1021/acsnano. 7b01306.

- [11]. Vishnoi, Pratap, K. Pramoda, and C. N. R. Rao. 2019. "2D Elemental Nanomaterials Beyond Graphene." ChemNanoMat 5(9):1062–91. doi: 10.1002/ cnma. 201900176.

- [12]. Das, Saptarshi, Amritanand Sebastian, Eric Pop, Connor J. McClellan, Aaron D. Franklin, Tibor Grasser, Theresia Knobloch, Yury Illarionov, Ashish V. Penumatcha, Joerg Appenzeller, Zhihong Chen, Wenjuan Zhu, Inge Asselberghs, Lain-Jong Li, Uygar E. Navakanta Avci. Bhat, Thomas D. Anthopoulos, and Rajendra Singh. 2021. "Transistors Based on Two-Dimensional Materials for Future Integrated Circuits." 4(11):786–99. Nature Electronics doi: 10.1038/s41928-021-00670-1.

- [13]. Mohanty, Sadhana Subhadarshini, Pradipta Dutta, and Jitendra Kumar Das. 2022. "A Dual Gate Material Tunnel Field Effect Transistor Model Incorporating Twodimensional Poisson and Schrodinger Wave Equations." International Journal of Numerical Modelling: Electronic Networks, Devices and Fields 35(1). doi: 10.1002/jnm.2933.

- [14]. Mendiratta, Namrata, and Suman Lata Tripathi. 2020. "A Review on Performance Comparison of Advanced MOSFET Structures below 45 Nm Technology Node." Journal of Semiconductors 41(6):061401. doi: 10.1088/1674-4926/41/6/061401.

- [15]. Wang, Binghao, Wei Huang, Lifeng Chi, Mohammed Al-Hashimi, Tobin J. Marks, and Antonio Facchetti. 2018. "High- k Gate Dielectrics for Emerging Flexible and Stretchable Electronics." Chemical Reviews 118(11):5690–5754. doi: 10.1021/ acs. chemrev.8b00045.