## Analyzing Work Function Dependency for Doping Variations in Double Gate Junction Less Field Effect Transistor: A TCAD Simulation Perception

Panchita Saikia<sup>1</sup>, Apurba Kumar Raibaruah<sup>2</sup>, Kaushik Chandra Deva Sarma<sup>3</sup> <sup>1</sup>Department of Instrumentation Engineering, CIT Kokrajhar, Kokrajhar -Assam, 783370, India. <sup>2</sup>Department of Instrumentation Engineering, CIT Kokrajhar, Kokrajhar-Assam, 783370, India. <sup>3</sup>Department of Instrumentation Engineering, CIT Kokrajhar, Kokrajhar-Assam, 783370, India. *Emails:* panchita.saikia29@gmail.com<sup>1</sup>, ak.raibaruah@cit.ac.in<sup>2</sup>, kcd.sarma@cit.ac.in<sup>3</sup>

#### Abstract

In this investigation, we present effect of work function on variation of electrical performance of conventional Double Gate Junctionless Field Effect Transistor (DGJLFET) for various range of doping profiles. By using TCAD simulator, the impact of doping concentrations spanning from 10<sup>10</sup> cm<sup>-3</sup> to 10<sup>19</sup> cm<sup>-3</sup> and work functions of 5.0 eV, 5.2 eV, and 5.4 eV is comprehensively explored. In this work the electrical parameters including threshold voltage, On Current, Off Current, On Current to Off Current ratio, and Subthreshold Swings are analyzed for each work function setting. Results indicate an interrelationship between higher doping levels and increased On Current, alongside a reduction in Subthreshold Swing. Notably, at a work function of 5.4 eV and a doping concentration of 10<sup>19</sup> cm<sup>-3</sup> threshold voltage obtained is 0.71 V, I<sub>ON</sub>/I<sub>OFF</sub> is 3.75 and Subthreshold Swing is 75 mV/decade are accomplished demonstrating the potential for optimized transistor performance through work function engineering.

*Keywords:* Doping profile; Junctionless Field Effect Transistor; On Current; Subthreshold swing; Threshold Voltage.

#### **1. Introduction**

Recently challenges have been made for fast scaling down of MOSFET. In order to continue with Moore's law, various devices of semiconductor have been suggested till date including nano structured devices such as quantum devices and high electron mobility devices. Also the size of MOSFET are reduced continuously in order to enhance the performance and low power consumption and thereby later on SCE (Short Channel Effect) are developed. Moreover various challenges have been confronted by lessening the size of the device thereby causing Short Channel Effects (SCE) such as drain induced barrier lowering (DIBL), channel length modulation, surface scattering, etc. In order to curtail all these SCE multigate MOSFETS were introduced [1-17]. However in order to overcome the challenges faced by SCE researchers have developed the proposal of Junction free transistor having uniform doping with no doping concentration gradients. The fabrication process and production cost of JLFET is less compared to Metal oxide FET [18]. Therefore, JLFETs seems to be a encouraging substitute to the standard MOSFETs [19]. Both the source and drain region proceeds towards each other to decrease the multigate MOSFET gate. Subsequently the channel is predominated by source, drain and gate which results in various SCEs in multigate MOSFET. Later on in order to overcome this difficulty, researchers proposed a new device naming Junctionless FET (JLFET). The foremost fabrication of JLFET was done by Collinge et. al. in the year 2009 [20]. Here source, channel and drains has a constant doping level. Mostly the silicon Junctionless nanowire transistor (JNT) is observed and considered to be one of the most favourable alternatives for future integrated circuits and has gained utter attention due to its

simple and easy fabrication process, extremely low short channel effects, near ideal subthreshold slope and having outstanding gate control ability [21-25].Moreover for scaling, low process flow and t has become most interesting semiconductor device. Therefore this VLSI design Junctionless Field Effect Transistors (JLFET) is gaining popularity in the field of VLSI design because of its various benefits over conventional MOSFET such as superior Ion/Ioff ratio, fast switching time, low power consumption, and excellent controllability of gate over the channel potential.One among them is the high off state current, carrier mobility degradation resulting from high doping concentration. It also has some major drawbacks which can be mitigated by the usage of a thin channel. With greater doping concentration the drain current produced will be larger, however the drawback is larger subthreshold slope which is also achieved due to wider channel preventing fulldepletion. But a thin channel will lower the on current creating the channel resistance to be high. Therefore JLFET can reduce SCE provided there is a very high doping profile in the substrate segment causing degradation in carrier mobility. The various conditions are necessary for turning the device off such as- a high work function variance between the channel and the gate region which also predominant in turning off the device. The device turn on current of JLFET is very high as the substrate is heavily doped. In this work a simulation method has been performed considering doping variation in DGJLFET based on different work functions. The study focuses on elucidating how variations in the work function impact on the performance of Double Junctionless Gate Field Effect Transistors (DGJLFET). Moreover, the study seeks to identify relationship between work function, doping concentration, and transistor performance metrics, providing insights into the underlying mechanisms governing DGJLFET behavior. Additionally, by pinpointing optimal combinations of work function and doping profile, the research aims to highlight strategies for enhancing the electrical performance of DGJLFETs, potentially paving the track for enhanced transistor designs in future semiconductor technologies.

#### 2. Structure and Simulation Setup

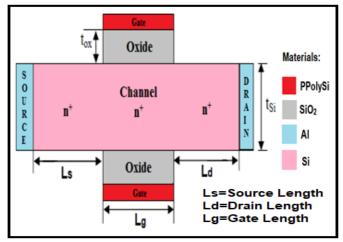

For simulation analysis a N-channel Double Gate Junctionless Field Effect Transistor has been considered. Figure.1 demonstrates the structural diagram of DGJLFET. The length of source and drain are considered as  $L_s = L_d = 10$  nm. In addition, the gate length  $(L_g)$  of device is considered as 10 nm. So, total size of the device is 30 nm. The thickness (t<sub>si</sub>) of the body of the device is 10 nm. The oxide thickness  $(t_{ox})$  is considered as 3 nm and gate thickness is 2nm. Work functions are considered as 5.0 eV, 5.2 eV and 5.4 eV. In this structure the doping is varied from  $10^{10}$  cm<sup>-3</sup> to  $10^{19}$  cm<sup>-3</sup>. For performing the simulation of various electrical parameters COGENDA Visual TCAD simulator is used considering Band to Band tunnelling for all simulations.

Figure 1 Schematic Diagram of DGJLFET

#### 3. Results And Discussions

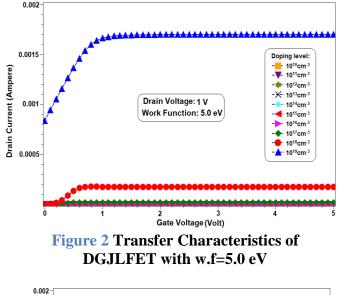

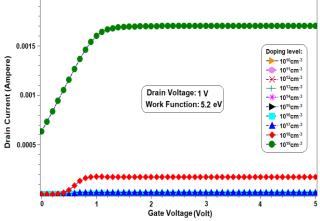

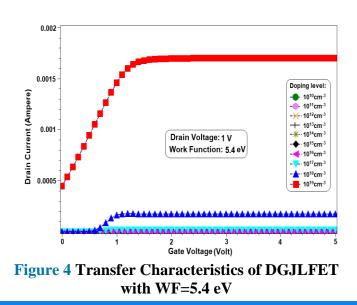

The transfer characteristics of doped DGJLFET for work functions 5.0 eV, 5.2 eV and 5.4 eV are presented in Figure 2, Figure 3 and Figure 4 respectively. From the above figures it can be observed that the drain current is maximum for doping at  $10^{19}$  cm<sup>-3</sup> for all the work functions. The On current is maximum at a value of 0.00168A for work function 5.0 eV, 0.001698 A for work function 5.2 eV and 0.00171 A for work function of 5.4 eV at a doping level of  $10^{19}$  cm<sup>-3</sup>. It has been observed that with higher work function ON current value is also high.

International Research Journal on Advanced Engineering Hub (IRJAEH) e ISSN: 2584-2137 Vol. 02 Issue: 09 September 2024 Page No: 2390 - 2402 https://irjaeh.com https://doi.org/10.47392/IRJAEH.2024.0328

Figure 3 Transfer Characteristics of DGJLFET with WF=5.2 eV

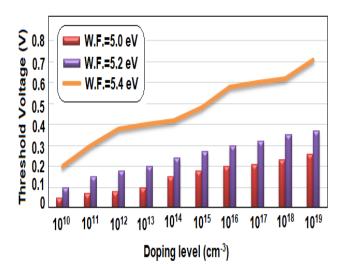

#### Figure 5 Threshold Voltage vs. Doping Level for Different Work Functions

From Figure 5 it can be analysed that the value of threshold voltage increases with an increase in work function value for different doping variation from  $10^{10}$  cm<sup>-3</sup> up to  $10^{19}$  cm<sup>-3</sup>. However, at work function 5.0 eV threshold voltage increases gradually with increases in doping level due to increase in dopant molecules. Similarly, for work function 5.2 eV and 5.4 eV as doping concentration increases due to increase in dopant level, threshold voltages also increases. For the study drain voltage is considered as 1 V.

# Table 1 ON Current for Different WorkFunctions at Different Doping Level

| DOPING                   | ON CURRENT             |                        |                        |

|--------------------------|------------------------|------------------------|------------------------|

|                          | WF=5.0                 | WF=5.2                 | WF=5.2                 |

|                          | (ev)                   | (ev)                   | (ev)                   |

| $10^{10} \text{cm}^{-3}$ | $4.28 \times 10^{-12}$ | $4.3 \times 10^{-12}$  | $4.31 \times 10^{-12}$ |

| $10^{11} \text{cm}^{-3}$ | $1.85 \times 10^{-10}$ | 1.87x10 <sup>-10</sup> | $1.88 \times 10^{-10}$ |

| $10^{12} \text{cm}^{-3}$ | $1.86 \times 10^{-10}$ | $1.88 \times 10^{-10}$ | $1.88 \times 10^{-10}$ |

| $10^{13} \text{cm}^{-3}$ | 1.85x10 <sup>-9</sup>  | 1.85x10 <sup>-9</sup>  | 1.88x10 <sup>-9</sup>  |

| $10^{14} \text{cm}^{-3}$ | 1.84x10 <sup>-8</sup>  | 1.89x10 <sup>-8</sup>  | 1.9x10 <sup>-8</sup>   |

| $10^{15} \text{cm}^{-3}$ | 1.88x10 <sup>-7</sup>  | 1.89x10 <sup>-7</sup>  | 1.9x10 <sup>-7</sup>   |

| $10^{16} \text{cm}^{-3}$ | 1.82x10 <sup>-6</sup>  | 1.88x10 <sup>-6</sup>  | 1.88x10 <sup>-6</sup>  |

| $10^{17} \text{cm}^{-3}$ | 1.83x10 <sup>-5</sup>  | 1.84x10 <sup>-5</sup>  | 1.85x10 <sup>-5</sup>  |

| $10^{18} \text{cm}^{-3}$ | 0.000175               | 0.000178               | 0.000179               |

| $10^{19} \text{cm}^{-3}$ | 0.00168                | 0.00169                | 0.00171                |

International Research Journal on Advanced Engineering Hub (IRJAEH)

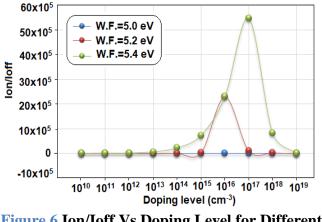

Figure 6 Ion/Ioff Vs Doping Level for Different Work Functions (W.F)

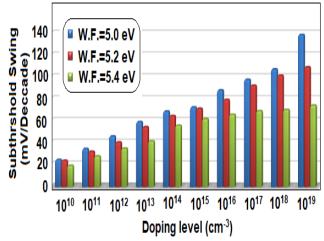

Table1 specifies ON current for different work function values with variation in doping concentration. It can be observed that increasing the doping level the ON current can be increased considering different work functions such as 5.0 eV, 5.2 eV and 5.4 eV respectively. At a doping level of  $10^{10}$  cm<sup>-3</sup> for work functions 5.0 eV, 5.2 eV and 5.4 eV ON current obtained are 4.28x10<sup>-12</sup> A, 4.3x10<sup>-12</sup> A and 4.31x10<sup>-12</sup> A respectively. On the other hand with increase in doping concentration we obtained ON current of 0.00168 A, 0.00169 A and 0.00171 A respectively. Figure 6 specifies Ion/Ioff ratio for different work function values with various doping concentration level. It has been observed that ON current OFF current ratio increases initially for work function 5.2 eV and 5.4 eV and after a certain doping level it starts decreasing as the off current increases. For work function 5.0 eV Ion/Ioff is very small. Figure 7 specifies Subthreshold Swing for different For the work functions doping level. all Subthreshold Swing increases as the doping level increases. But with work function 5.4 eV Subthreshold Swing has a lesser value compared to the work functions 5.0 eV and 5.2 eV. At a doping level of  $10^{19}$  cm<sup>-3</sup> for work function 5.4 eV Subthreshold Swing obtained is 75 mV/decade. Subthreshold Swing is calculated by using the formula-

SubthresholdSwing =

$$\frac{\partial V_g}{\partial (\log I_d)}$$

Where  $dV_g$  is the change in gate voltage and  $I_d$  is drain current.

Figure 7 Subthreshold Swing Vs Doping Level for Different Work Functions (W.F.)

The study examines a comprehensive analysis of the effect of work functions on DGJLFET functionality across a wide range of doping profiles, providing a thorough understanding of their interplay. Through the illustration of significant performance achievements, such as the attainment of a threshold voltage of 0.71 V,  $I_{ON}/I_{OFF}$  ratio of 3.75, and Subthreshold Swing of 75 mV/decade at specific work function (5.4 eV) and doping levels of  $10^{19}$  cm<sup>-3</sup>, the study highlights avenues for optimizing DGJLFET designs for enhanced functionality and efficiency. **Conclusion**

The present work systematically investigated the impact of work function variations on the electrical performance of conventional Double Gate Field Effect Junctionless Transistors (DGJLFETs) across a range of doping profiles. Through comprehensive analysis of transfer characteristics, On Current, Ion/Ioff ratio, and Subthreshold Swing using TCAD simulation for work functions of 5.0 eV, 5.2 eV, and 5.4 eV were explored in conjunction with doping levels ranging from  $10^{10} \text{ cm}^{-3}$  to  $10^{19} \text{ cm}^{-3}$ . The findings reveal that higher doping levels, particularly at  $10^{19} \text{ cm}^{-3}$ , leads to favorable On Current

International Research Journal on Advanced Engineering Hub (IRJAEH) e ISSN: 2584-2137 Vol. 02 Issue: 09 September 2024 Page No: 2390 - 2402 https://irjaeh.com https://doi.org/10.47392/IRJAEH.2024.0328

IRJAEH

characteristics across varied work function spectra. Notably, a Subthreshold Swing of 75 mV/ decade was accomplished at a work function of 5.4 eV, emphasizing the importance of high work functions in minimizing Subthreshold Swing. In conclusion, the results suggest that DGJLFETs exhibit superior electrical properties, particularly in terms of On Current, when operated with higher work functions. This emphasizes the significance of work function engineering in enhancing the performance of DGJLFET devices.

### References

- Lee, C. W., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., and Colinge. J.P. (2009).Junctionless multigate field effect transistor. Applied Physics Letters, 94(5), 053511-053512 .doi:10.1063/1.3079411

- [2]. S. Migita, Y. Morita, T. Matsukawa, M. Masahara, and H. Ota,(2014).Experimental demonstration of ultrashort-channel (3 nm) junctionless FETs utilizing atomically sharp V-grooves on SOI.IEEE Transactionon.Nanotechnology,13(2),2082 15.doi: 10.1109/TNANO.2013.2296893

- [3]. R. Rios et al., (2011).Comparison of junctionless and conventional trigate transistors with Lg down to 26 nm. IEEE Electron Device Letter, 32(9),1170-1172.doi: 10.1109/led.2011.2158978

- [4]. I.-H. Wong, Y.-T. Chen, S.-H. Huang, W.-H. Tu, Y.-S. Chen, and C. W. Liu, (2015).Junctionless gate-all-around pFETs using in-situ borondopedge channel on Si. IEEE Transaction Nanotechnology,14(5),878–882. doi: 10.1109/TNANO.2015.2456182.

- [5]. A.K. Raibaruah, K.C.D. Sarma,(2021).A

Potential Model for Parallel Gated

Junctionless Field Effect Transistor.

Silicon, Springer,14(2), 711-718.

doi:10.1007/s12633-020-00890-8.

- [6]. A. K. Raibaruah and K. C. D. Sarma,(2020). Parallel Gated Junctionless Field Effect Transistor.In International Conference on Computational Performance Evaluation (ComPE), North Eastern Hill

University, Shillong, India.doi: 10.1109/ ComPE49325.2020.9200029

- [7]. Park, C. H., Ko, M.D., Kim, K.H., Baek, R.H., Sohn, C.W., Baek, C.K., Park, S., Deen, M.J., Jeong, Y.H., and Lee, J.S. (2012).Electrical characteristics of 20nm junctionless Si nanowire transistors. Solid-State Electronics, 73,7– 10.doi:10.1016/j.sse.2011.11.032.

- [8]. Gnudi, A., Reggiani, S., Gnani, E. and Baccarani, G. (2012). Analysis of threshold voltage variability due to random dopant fluctuations in junctionless FETs. IEEE Electron Device Letters, 33(3), 336–338. doi: 10.1109/LED.2011.2181153.

- [9]. A.Talukdar, A. K Raibaruah, K.C.D Sarma,(2020).Dependence of Electrical Characteristics of Junctionless FET on Body Material.Third International Conference on Computing and Network Communications (CoCoNet'19), Procedia Computer Science, 171,10461053.doi:10.1016/j.procs.2020 .04.112.

- [10]. Chiang, T. K.,(2012).A quasi-twodimensional threshold voltage model for short-channel junctionless double-gate MOSFETs. IEEE Transactions on Electron Devices, 59(9), 2284–2289. doi: 10.1109/TED.2012.2202119.

- [11]. Gnudi, A., Reggiani, S., Gnani, E. and Baccarani, G.(2013).Semi analytical Model of the Subthreshold Current in Short-Channel Junctionless Symmetric Double-Gate Field-Effect Transistors.IEEE Transactions on Electron Devices, 60(4),1342-1348. doi: 10.1109/TED.2013.2247765.

- [12]. A.K. Raibaruah, K.C.D. Sarma (2022).Junctionless Field Effect Transistor with Undoped and Doped profile- A Comparative Study.IEEE Delhi Section Conference(DELCON).doi: 10.1109/DE LCON54057.2022.9753590

International Research Journal on Advanced Engineering Hub (IRJAEH)

- [13]. A. K Raibaruah, A. Talukdar and K.C.D Sarma(2020) .Undoped Junctionless Field Effect Transistor.In International Conference on Computational Performance Evaluation (ComPE), North Eastern Hill University,Shillong,India.doi: 10.1109/Co mPE49325.2020.9200000

- [14]. Li, C., Zhuang, Y., Di, S., and Han, R.(2013) .Subthreshold Behaviour Models for Nanoscale, Short-Channel Junctionless Cylindrical Surrounding-GateMOSFETs.IEEE Transactions on Electron Devices, 60(11),3655-3662.doi: 10.1109/TED.2013.2281395.

- [15]. A.K. Raibaruah, K.C.D. Sarma ,(2022). Digital Circuit Performance Evaluation of Parallel Gated Junctionless Field Effect Transistor. Journal of Nanoelectronics and optoelectronics,17(3),374-382doi:10.1166/jno.2022.3235.

- [16]. A.K. Raibaruah, K.C.D. Sarma (2022).Carrier mobility analysis of Parallel Gated Junctionless Field Effect Transistor.Journal of Nanoelectronics and optoelectronics,17(1),1-12. doi:10.1166/jno.2022.3163

- [17]. A.K. Raibaruah, K.C.D. Sarma (2022).An Analytical Model for the Depletion Region Width and Threshold Voltage of a Parallel Gated Junctionless Field Effect Transistor.Journal of Nano- and Electronic Physics, 14 (4), 04005 (1-5). doi: 10.21272/jnep.14(4).04005

- [18]. S. Sahay and M. J. Kumar, Volume (2016).Realizing Efficient Depletion in SOI Junctionless FETs. IEEE Journal of the Electron Devices Society,4(3),110-115. doi: 10.1109/JEDS.2016.2532965.

- [19]. K. Kumar,(2022).Comparative Study of Symmetric and Asymmetric Oxide Double Gate Junction less FET.Journal of Electrical Engineering, Electronics, Control and Computer Science – JEEECCS, 8(28), 25-28.

- [20]. Colinge J.P., Lee, C.W., Afzalian, A., Dehdashti, N., Yan, R., Ferain, I., Razavi, P., O'Neill, B., Blake, A., White, M., Kelleher, A.M., McCarthy B., and Murphy R(2009). SOI Gated Resistor: CMOS without Junctions.IEEE International SOI Conference,Foster City, California,USA.doi: 10.1109/SOI.2009.

- 5318737 [21]. Raskin, J. P., Colinge, J. P., Ferain, I., Kranti, A., Lee, C. W., Dehdashti, N., Yan, R., Razavi, P., and Yu., R.(2010).Mobility Improvement in Nanowire Junctionless Transistors by Uniaxial Strain. Applied Physics Letters, 97(4). 042114. Doi: 10.1109/SOI.2010.5641390

- [22]. Colinge, J.P. and Colinge, C.A.(2011) Physics of Semiconductor Devices.Kluwer Academic Publishers.

- [23]. Trevisoli, R.D., Doria, R.T., de Souza, M., Das, S., Ferain, I., and Pavanello, M.A.,(2012) Surface potential based drain current analytical model for triple gate junctionless nanowire transistors.IEEE Transactions on Electron Devices,59(11),3510–3518. doi: 10.1109/TED.2012.2219055

- [24]. Lou, H., Zhang, L., Zhu, Y., Lin, X., Yang, S., He, J., and Chan M.(2012) .A junctionless nanowire transistor with a dual-material gate. IEEE Transactions on Electron Devices, 59(7), 1829–1836. doi: 10.1109/TED.2012.2192499.

- [25]. Colinge, J. P., Kranti, A., Yan, R., Lee, C.W., Ferain, I., Yu, R., Akhavan, N.D., and Razavi P.,(2011).Junctionless Nanowire Transistor (JNT): Properties and design guidelines.Solid-StateElectronics, 65–66, 33-37.doi:10.1016/j.sse.2011.06.004.